Hochschulschrift

Dynamisch und partiell rekonfigurierbare Hardwarearchitektur mit adaptivem hardwaregestützten Routing zur Laufzeit

- Location

-

Deutsche Nationalbibliothek Frankfurt am Main

- Extent

-

Online-Ressource

- Language

-

Deutsch

- Notes

-

Karlsruhe, Karlsruher Institut für Technologie (KIT), Diss., 2015

- Classification

-

Informatik

- Keyword

-

Architektur

Modul

Prozessor

Rekonfiguration

CUDA

Grafikprozessor

Anwendungsspezifischer Prozessor

FLOPS

CPLD

CISC

Datenpfad

CMOS

- Event

-

Veröffentlichung

- (where)

-

Karlsruhe

- (who)

-

KIT-Bibliothek

- (when)

-

2015

- Creator

- Contributor

-

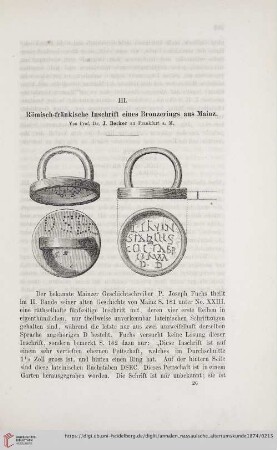

Becker, J.

- URN

-

urn:nbn:de:swb:90-536676

- Rights

-

Der Zugriff auf das Objekt ist unbeschränkt möglich.

- Last update

-

14.08.2025, 10:54 AM CEST

Data provider

Deutsche Nationalbibliothek. If you have any questions about the object, please contact the data provider.

Object type

- Hochschulschrift

Associated

- Thomas, Alexander

- Becker, J.

- KIT-Bibliothek

Time of origin

- 2015